Serviços Personalizados

Journal

Artigo

Indicadores

-

Citado por SciELO

Citado por SciELO

Links relacionados

-

Similares em

SciELO

Similares em

SciELO

Compartilhar

Revista de Ciencia y Tecnología

versão On-line ISSN 1851-7587

Rev. cienc. tecnol. no.22 Posadas dez. 2014

ÁREA: INGENIERÍA, TECNOLOGÍA E INFORMÁTICA

Implementacion de un modulo IP de un circuito de lazo de costas para demodular senales BPSK en sistemas FPGA de Xilinx

Implementation of a costas loop IP module to demodulate BPSK signals in Xilinx FPGA Circuits

Juan R. Rodriguez Suarez1,*, Carlos Corvea Armenteros1, Jorge Torres Gomez2

1 Departamento de Telecomunicaciones y Electronica, UPR, Cuba.

2 Departamento de Telecomunicaciones, ISPJAE, Cuba.

* E-mail: jotar@tele.upr.edu.cu

Resumen

Este trabajo presenta el diseno e implementacion de un modulo IP de un circuito de Lazo de Costas para demodular senales BPSK, realizado sobre la base del empleo la biblioteca XSG de Xilinx sobre Matlab. Se parte del diseno de un modelo Simulink para el circuito de Lazo de Costas que permite ajustar los parametros necesarios del modelo para demodular una senal BPSK. Este modelo se transforma a uno equivalente con bloques de la biblioteca XSG a fin de generar el modulo IP del circuito de Lazo de Costas que puede ser empleado en un sistema con el procesador empotrado MicroBlaze. Se presenta una metodologia para demodular una senal BPSK que comprende tres etapas: el pre-procesamiento de la senal BPSK, la aplicacion del circuito del Lazo de Costas y el post-procesamiento de la senal obtenida con dicho Lazo a fin de obtener la secuencia de bits. Se presentan los resultados en senales simuladas y reales.

Palabras clave: Lazo de Costas; Demodulacion BPSK; Modulo IP; FPGA; MicroBlaze.

Abstract

This paper is about the design and implementation of a Costas Loop IP Module to demodulate BPSK. It was designed using theMatlab Simulink XSG Library.The starting point was the design of a Simulink model of the Costas Loop Circuit to adjust the parameters needed to demodulate a BPSK signal. This model is transformed to an equivalent but it was built only with blocks of Xilinx XSG library in order to generate the IP module to be used with a MicroBlaze embedded microprocessor. A three stages procedure is presented to demodulate a BPSK signal: a pre-processing of the BPSK signal, the Costas Loop application to obtain the in- phase signal and the post-processing of this signal to recover the bit sequence. Results with simulated and real signals are analyzed.

Keywords: Lazo de Costas; BPSK de-modulation; IP Module; FPGA; MicroBlaze.

Introduccion

Actualmente los sistemas de telecomunicaciones se pueden implementar mediante técnicas digitales, lo cual permite diseñar un sistema casi íntegramente en un sistema digital, y acercar más hacia la antena las etapas de procesamiento digital de la señal eliminando o reduciendo los componentes analógicos del sistema. Esta técnica es conocida como radio definido por software (SDR) (1). El procesamiento digital se puede implementar típicamente en hardware mediante la programación de procesador digitalsecuencial con una arquitectura definida DSP (2) o mediante un procesador con arquitectura específica de acuerdo al procesamiento digital necesario.

En este trabajo se presenta el diseño digital del circuito conocido como Lazo de Costas, ampliamente usado en la demodulación de señales digitales, que es implementado sobre un circuito de hardware reconfigurable FPGA de la familia Spartan 3E de Xilinx. El circuito ha sido diseñado sobre la filosofía de un módulo de propiedad intelectual IP que puede ser usado repetidas veces, para procesar modulaciones del tipo BPSKen la banda de audio con frecuencias de muestreo de hasta 4400 kHz.

Materiales y metodos

Para este trabajo se empleó una tarjeta Nexys2 (3), que contiene un procesador FPGA xc3s1200 de Xilinx, y otros periféricos. El desarrollo de las aplicaciones FPGA y del móduloIP se realizó con los ambientes de diseño ISE v12.4 y XPS v12.4 de Xilinx y el programa Matlab versión R2009b con uso de las bibliotecas respectivas de Simulink y XSG. La aplicación de comunicación con la tarjeta Nexys2 y la computadora se realizó con el programa de Instrumentación Virtual LabWindows/CVI v 9.0.

Senales BPSK

La modulación por desplazamiento de fase binaria o BPSK (Binary Phase Shift Keying) es una forma de modulación angular que consiste en hacer variar la fase de una portadora en dos valores discretos manteniendo amplitud y frecuencias constantes. Entre las modulaciones digitales de fase esta es la de mayor inmunidad al ruido, puesto que la diferencia entre símbolos en la constelación es máxima (180º). Dichos símbolos suelen tener un valor de salto de fase de 0º para el 1 lógico y 180º para el 0 lógico. En cambio, su velocidad de transmisión es la más baja de las modulaciones de fase. Es una forma de transmisión pasa banda, el flujo de datos digitales se modula en una portadora sinusoidal de frecuencia fc y amplitud constante (4). Una señal BPSK(t) se puede generar alternativamente a partir de una secuencia de bits Data(t), expresada en el formato bipolar sin retorno cero con niveles lógicos [+1, -1] como:

![]()

Si se conociera la señal portadora de forma coherente, entonces la señal demodulada Dem_BPSK(t) que permite recuperar la secuencia de bits Data(t), pudiera implementarse con simplemente multiplicar por la señal portadora y filtrar paso bajo para eliminar el término relativo al tono del doble de la frecuencia portadora resultante:

CIRCUITO DE LAZO DE COSTAS

En el caso de las modulaciones BPSK aparece el problema de que la portadora no se transmite, y por lo tanto no es posible demodular filtrando la señal modulada como se expresa en la ecuación 3. El circuito de Lazo de Costas es una de las técnicas más usadas para la demodulación de señales BPSK y se basa en la demodulación coherente (5) (6), donde se regenera la señal portadora con fase y frecuencia similares a la que se recibe empleó en su modulación. En la figura 1, se muestra el esquema del circuito de Lazo de Costas de tipo analógico: la señal de entrada BPSK se aplica a dos detectores de fase idénticos -compuestos cada uno por un multiplicador y un filtro paso bajo-; la salida de los detectores de fase I, Q es multiplicada por M3 y después filtrada por F3, y por último es aplicada a un oscilador controlado por voltaje VCO. Según esta configuración se tienen dos canales de salida en cuadratura para las señales I y Q.

Figura 1: Circuito de Lazo de Costas.

Este esquema se deriva de los conceptos de realimentación relacionados con los circuitos de control por Lazo de Fase (7) (8). Cuando el oscilador local se ajusta a la frecuencia de la portadora y mantiene una diferencia de fase muy pequeña con la misma, se dice que está enganchado como es usual en los circuitos PLL, sin embargo en este caso las pequeñas variaciones en los errores de voltaje en el lazo o bucle de Costas se procesan al doble de sensibilidad puesto que la señal de error tiene periodicidad en π. Esto hace que el bucle de Costas sea especialmente adecuado para los desplazamientos de frecuencia de la portadora (5).

La señal a la salida del mezclador M1 se deriva por un procedimiento similar al obtenido en la ecuación 3, considerando una secuencia de bits bipolar m(t), pero asumiendo fases distintas θ1y θ2 para el oscilador local y la portadora:

![]()

Similarmente a la salida del mezclador M2 se obtiene:

![]()

Las señales asociadas a los multiplicadores M1 y M2 son procesadas por los filtros paso bajo F1, F2 que atenúan los términos relativos al doble de la frecuencia de la portadora de las ecuaciones 7, 8 pero dejan pasar los términos de la diferencia de fase y el ancho de banda del mensaje. La salida del filtro F1 se denomina señal I y la del filtro F2 señal Q. Si el oscilador local se logra sintonizar a una diferencia de fase muy pequeña con la portadora entonces la señal I es proporcional al mensaje y la señal Q tiende a cero. En el tercer mezclador M3 se obtiene entonces una señal relativa a la diferencia de fase

El filtro del Lazo F3 remueve la componente de alta frecuencia restante, y se tiene en cuenta que el cuadrado de la señal mensaje binaria m(t) es 1. Haciendo una analogía con el circuito PLL se tiene entonces que la salida de error de fase viene dada por la salida del filtro de Lazo F3 y esta es la señal de error que se aplica al oscilador local. Esto hace que el circuito de Lazo de Costas produzca dos puntos de enganche: 0 y π, que producen las salidas necesarias para que el VCO genere las fases y frecuencias necesarias [5]. Como la modulación BPSK presenta cambios de fase de 180o a la entrada del lazo, que es el próximo período donde la función de detección de fase tiene una respuesta idéntica, se puede asegurar que el lazo será capaz de rastrear una portadora con modulación BPSK. El oscilador local VCO genera una señal coseno en el tiempo, dada por:

![]()

Donde fc es la frecuencia, φ es la fase inicial, kc la ganancia del oscilador en Hz/V y u(t) es la señal de voltaje de entrada que es integrada a fin de producir el ajuste de la fase necesario. En el lazo de Costas, la señal u(t) es la señal a la salida del filtro F3 que procesa la salida del multiplicador M3: la señal proporcional a la diferencia de fase correspondiente a la ecuación 9.

Criterios para el diseno de un lazo de costas digital

Se puede extrapolar el circuito analógico del Lazo de Costas a uno digital, partiendo de una señal modulada BPSK, digitalizada con una cierta frecuencia de muestreo fm, si se implementan los mutiplicadores y filtros en hardware digital y un oscilador numérico como oscilador local. Los parámetros básicos del Lazo de Costas son:

• Tiempo de establecimiento.

• Rango de enganche (looprange) y captura.

• Funcionamiento ante el ruido.

El tiempo de establecimiento del lazo es el tiempo que demora el oscilador NCO en generar una señal con la fase y frecuencia correctas de forma tal que sea idéntica a la señal de entrada (6), (8). Los rangos de enganche y captura en cuanto a definición, de los circuitos de Lazo de Costas, son idénticos a los descritos para los PLL. Según la revisión bibliográfica realizada, se ha podido comprobar que no existe un procedimiento analítico de diseño establecido que permita calcular todos los parámetros necesarios en la configuración del bucle de Costas. La mayoría de los autores (9), (10) recomiendan el ajuste de los parámetros mediante los resultados de la simulación. Para un diseño digital del circuito de Lazo de Costas para demodular señales BPSK se necesita ajustar convenientemente los parámetros de operación de sus distintos bloques a fin de lograr la demodulación correcta de la señal. Estos son:

Filtros paso bajo de rama F1 y F2 asociados a los mezcladores M1 y M2

Los filtros paso bajo de la rama superior e inferior deben de ser capaces de eliminar las componentes del doble de la frecuencia de la portadora 2 fc, así como tener un ancho de banda de paso mínimo para dejar pasar el ancho de banda del mensaje m(t) que es función del tiempo de bit Tb.Estos filtros junto con los multiplicadores respectivos M1, M2 conforman los detectores de fase respectivos de cada rama.

Filtro F3 del lazo, paso bajo, que procesa la senal de error a la salida del mezclador M3

Este filtro remueve componentes de alta frecuencia presentes en la señal diferencia de fase obtenida a la salida del multiplicador M3.

Oscilador local NCO

Este oscilador tiene dos parámetros de ajuste, la frecuencia de oscilación central fc y la ganancia de fase kc según la ecuación 10. La frecuencia de oscilación se selecciona como la frecuencia de la portadora y la ganancia de fase kc es el parámetro decisivo en el ajuste del Lazo de Costas, junto con la banda de paso del filtro F3. Este valor se impone como un factor de ganancia de salida del filtro F3. Teniendo en cuenta lo antes expuesto, en realidad no puede implementarse el circuito del Lazo de Costas para demodular señales BPSK, sin información previa de la modulación de la misma. Es necesario entonces un pre-procesamiento de la señal modulada para extraer valoraciones de la frecuencia de la portadora fc y del tiempo de bit Tb de la secuencia de datos digital.

Modelo simulink para el lazo de costas digital

Partiendo del esquema del lazo de Costas expuesto en la figura 1, se puede construir directamente un modelo equivalente en el programa Simulink de Matlab. Esto es ventajoso debido a la disponibilidad de herramientas para el diseño de filtros digitales y el análisis de las señales procesadas en el dominio del tiempo y de la frecuencia que presenta este programa. Además de poder importar señales reales en este ambiente, también se pueden generar señales simuladas BPSK, con los valores de frecuencia de portadora fc, tiempo de bit Tb y relación señal ruido SNR necesarios a fin de evaluar su comportamiento y ajustar convenientemente el circuito de Lazo de Costas. El modelo simulink del Lazo de Costas se presenta en la figura 2, basado en el circuito original del Lazo de Costas de la figura 1. La señal BPSK está digitalizada a una frecuencia de muestreo fm - típicamente de 44100 Hz- todos los filtros se implementan digitalmente por una ecuación en diferencias con un diseño de acuerdo a los requerimientos anteriormente discutidos.

Figura 2: Modelo simulink de Lazo de Costas.

Para el oscilador local el bloque de Matlab se basa en el método de tabla ROM (11) usado para generar señales en procesadores y sintetizadores digitales. Este método de generación facilita la implementación posterior de dicho oscilador en hardware. Para ello se almacenan en memoria ROM, un número de puntos D correspondientes al período fundamental de la señal que se desea generar, tomados con una determinada frecuencia de muestreo fm. Las direcciones de memoria se relacionan con la fase de la señal, por lo que recorriendo las mismas con un intervalo K1 dado se puede generar una señal con frecuencia fo, K1 veces superior al período fundamental de la señal de baja frecuencia almacenada, dada por la ecuación:

![]()

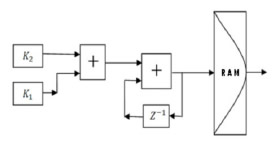

El recorrido de las direcciones de memoria ROM se expresa en hardware por un acumulador con intervalo K1. Esta constante define la frecuencia fc de referencia del oscilador. La constante K2 define la ganancia de fase del oscilador. Se ha incluido un sumador a la entrada del acumulador a fin de considerar el control de la fase por el voltaje. Se suma a la constante K1 el producto de la constante K2 por la señal de error de fase u(n) filtrada. La arquitectura en hardware del oscilador local se presenta en la figura 3 y la ecuación del oscilador numérico por la ecuación 12.

![]()

Figura 3: Generador NCO implementado con una tabla RAM de datos almacenados.

Donde ωo es la frecuencia discreta central del oscilador local. Se nota que la constante original kc de la ganancia del oscilador local expresada en unidades de frecuencia por voltaje [Hz/V] , cambia como kc T, con unidades de fase por voltaje [rad/V], teniendo en cuenta el efecto del muestreo en el tiempo T. Para un número de puntos D expresado como una potencia N de 2 se tiene entonces que las constantes k1 y k2 del acumulador se calculan como:

Los dos filtros de rama F1 , F2 se han implementado como filtros FIR, con una banda de paso que contenga el espectro del mensaje que depende de la frecuencia de bits y una banda de paso que atenúe el doble de la frecuencia portadora 2ωo. Con estos criterios y empleando los métodos disponibles de diseño de filtros, por ejemplo el método de la ventana, se pueden calcular los M coeficientes de dichos filtros e implementar su ecuación en diferencias. El filtro del lazo F3 se ha implementado como un filtro IIR orden 1, con un polo real a y un cero en la frecuencia discreta π, a fin de obtener un filtro paso bajo con respuesta de frecuencia normalizada a la unidad en la frecuencia discreta cero. Mientras más cercano a la unidad sea el polo real a, el filtro atenuará más las frecuencias alejadas de la componente de directa de la señal de error de salida del mezclador M3. La función del sistema de dicho filtro H(z) es:

Modelo en hardware para el lazo costas digital

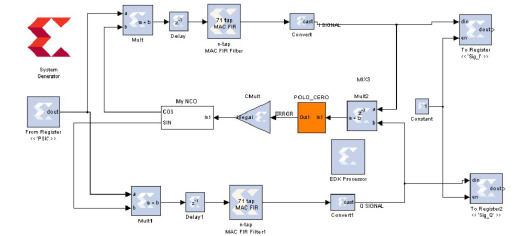

La construcción del modelo en hardware para ser sintetizado en un circuito FPGA se realiza sobre la base de exportar el modelo Simulink-Matlab anteriormente descrito a un modelo equivalente, pero empleando únicamente los bloques de la biblioteca XSG. Esta biblioteca permite que desde el ambiente de Matlab se realice completamente el proceso de generación de hardware para dispositivos FPGA de Xilinx. En la figura 4 se presenta dicho diseño. Se trabaja con aritmética de punto fijo con formato bipolar de 16 bits de palabra y 15 de fracción y una frecuencia de muestreo de 44100 Hz. Se emplean tres multiplicadores dedicados de 18 bits para la implementación de los mezcladores respectivos.

Figura 4: Modelo XSG del Lazo de Costas.

El diseño del oscilador local que genera la portadora se muestra en la figura 5. Se aprecian dos bloques de memoria ROM que almacenan 216 valores de la funciones coseno y seno con una frecuencia fundamental de 0.6729 Hz, el acumulador y el sumador a su entrada. La constante especificada K1 garantiza la frecuencia de la portadora necesaria según la ecuación 13. La entrada del oscilador es la señal de error multiplicada por la ganancia de fase especificada por la constante K2 y las dos salidas se refieren a las salidas de la señales coseno y seno. Para implementar los FIR de rama, como estos pueden requerir órdenes elevados, se ha usado una estructura del tipo MAC [12] multiplicador - acumulador, que permite emplear un solo multiplicador dedicado para cada filtro, por lo que estos bloques en realidad trabajan a una frecuencia de muestreo que es M veces superior a la frecuencia del sistema, donde M es el orden del filtro. Los coeficientes de los filtros y los valores de las entradas retardadas se almacenan en bloques de memoria que alimentan el multiplicador acumulador en cuestión.

Figura 5: Modelo XSG del oscilador local del Lazo de Costas.

El filtro IIR del lazo se implementa según la estructura cero-polo descrita anteriormente, empleando una forma directa 1. En este caso no es necesario emplear multiplicadores dedicados, se emplean multiplicadores en lógica distribuida teniendo en cuenta que uno de los factores de la multiplicación es constante por ser uno de los coeficientes del filtro en cuestión. Para generar el bloque IP se emplea la metodología estándar que se especifica para la biblioteca XSG (13), por ello se han incluido el bloque de registro de entrada <PSK>, los bloques de registros de salida <Sig_I> y <Sig_Q> y el bloque del procesador EDK. Estos registros definen la forma que un procesador empotrado MicroBlaze interactúa con el hardware sintetizado (bloque IP) del Lazo de Costas. Cada registro en el diseño incluye registros compartidos de entrada y salida, pues se trata de registros compartidos por el bloque IP y el procesador. De esta forma cuando en el programa del procesador se escribe en el registro PSK, se pueden transferir los valores de la modulación que estén almacenados en memoria y que son inmediatamente leídos por el IP del Lazo de Costas. A la salida del lazo se escriben en los registros Sig_I, Sig_Q los valores correspondientes de las señales en cuadratura I, Q del Lazo que pueden entonces ser leídos por el procesador. Se compila el modelo con la opción de sintetizar el módulo IP y exportarlo hacia EDK, esto genera un conjunto de ficheros que comprenden toda la síntesis del módulo IP, así como la documentación para ser usado directamente en un proyecto XPS con un procesador empotrado MicroBlaze. Una vez sintetizado el hardware de la aplicación en XPS, se puede diseñar un software que aplique el mismo, donde en lo fundamental es necesario escribir primero en el registro compartido relativo a la señal BPSK y leer en los registros relativos a las señales I, Q que han sido calculadas por el IP core en cuestión.

Analisis de los resultados

Teniendo en cuenta las posibilidades que nos brindan los modelos explicados anteriormente, para la demodulación de señales simuladas y reales, se realizaron un conjunto de experimentos a fin de evaluar el comportamiento de dichos modelos.

• Efecto de la diferencia de fase entre portadora y oscilador

Cuando la fase de la portadora y la del NCO son iguales el lazo procesa perfectamente la señal de entrada. Sin embargo para acercar un poco más el modelo al trabajo en condiciones reales se requiere variar la fase inicial de la portadora en la generación simulada y valorar como el oscilador local, producto de la realimentación de la diferencia de fases, es capaz de ajustarse hasta lograr generar la portadora exacta. En la figura 6 se presenta una señal simulada de una portadora de 5300 Hz con fase de 90º y la señal del oscilador NCO, donde se aprecia como éste último realiza el ajuste de fase necesario a medida que el tiempo transcurre, en un tiempo menor que Tb.

Figura 6: Enganche del oscilador local con la portadora.

• Efecto de la diferencia de frecuencias entre portadora y oscilador

La figura presenta el resultado de la simulación donde se muestra la evolución de la señal de error de fase a la entrada del oscilador local, para una portadora fija de 5300 Hz y diferentes frecuencias del oscilador local en el intervalo de 5150 a 5450 Hz. Se ha supuesto una diferencia entre la frecuencia del oscilador local y la frecuencia real de la portadora a 5300 Hz, se presenta la variación en tiempo de la señal de error de entrada al oscilador local u(n) que se corresponde con la diferencia de fases. Se aprecia el enganche del oscilador cuando la diferencia de frecuencias es de hasta 150 Hz, con señales de error constantes en el tiempo después de un régimen transitorio.

Figura 7: Senal de error en funcion del tiempo segun diferencias en frecuencias.

• Efecto de la relación señal ruido en el canal

Cuando disminuye la relación SNR en el canal de transmisión la señal BPSK se distorsiona apreciablemente. En la figura 11 se aprecian las salidas I, Q correspondiente a una señal BPSK con portadora a 4410 Hz, Tb=1/882 s y señal ruido SNR=10, para varias valores de ganancia del lazo kc desde 500 hasta 5000 Hz/V. Se aprecia como la señal I se distorsiona notablemente por el ruido y como con la ganancia de 5000 Hz se producen resultados incorrectos en la demodulación. Así mismo la señal Q también se distorsiona y se incrementa sus valores apreciablemente respecto a valor teórico cercano a cero.

Figura 8: Senales I para una demodulacion con baja SNR en funcion de la ganancia del lazo.

Figura 9: Raster de senal con sincronismo.

Figura 10: Senales I para aplicaciones con osciladores locales de 16 bits y 12 bits de acumulador.

Figura 11: Senales I para modelos Simulink, XSG y con IP de Costas (reales)

Estos resultados muestran que se necesita entonces un post-procesamiento después que se han extraído las señales I, Q con el esquema del lazo de Costas, para poder recuperar correctamente la secuencia de bits.

• Recuperación de los bits recibidos

El tiempo de símbolo se determina a partir del criterio de que éste será el símbolo que más se repita cuando se analiza una secuencia de larga duración. Esto se realiza por medición directa de las muestras entre cruces por cero. La probabilidad de ocurrencia del envío elemental está dada por la probabilidad de la secuencia "010" o "101". Los pasos para la determinación del tiempo de símbolo son los siguientes (14):

1. Medición en muestras de los cruces por cero y conformación del histograma.

2. Determinación en el histograma del envío que más se repite.

3. Rectificación de los envíos menores que el elemental.

4. Nueva medición en muestras de los cruces por cero y conformación del histograma.

5. Determinación en el histograma del envío que más se repite y cálculo de su promedio.

6. Comparación del envío elemental con las transiciones encontradas, con esto se conforma la secuencia de datos recibida.

Además en señales reales normalmente se transmiten patrones de secuencias de bits intercalados en el mensaje con determinada periodicidad lo que pueden ser visualizados adecuadamente si se crea una imagen de la secuencia de bits asociándoles niveles de negro y blanco a los niveles de bits. Esta imagen se denomina raster. Este método es muy poderoso, pues permite hacer una evaluación preliminar de la demodulación mediante una visualización en una imagen de sus patrones de sincronismo.

Los resultados anteriormente expuestos fueron obtenidos en base a la simulación. Para comprobar el correcto funcionamiento del módulo IP del lazo de Costas, se implementó un procesador MicroBlaze MB en una tarjeta Nexys2. Este procesador fue diseñado con diversos periféricos entre ellos un módulo de comunicación RS232, un temporizador, una memoria RAM y el módulo IP del Lazo de Costas explicado anteriormente. Para comprobar el funcionamiento del módulo IP del lazo de Costas, el procesador se comunica con una PC, en la que se almacenan inicialmente los datos de las señales BPSK. Estos datos son enviados hacia el procesador MB mediante comunicación RS232 y almacenados en memoria RAM. Una subrutina de interrupción del temporizador se dispara con un tiempo equivalente al tiempo de muestreo, envía un dato almacenado en memoria hacia el módulo IP del lazo, y re-almacena el resultado del procesamiento (señal I) en la misma localización de memoria. Cuando se han terminado de procesar todos los datos, se transmiten los resultados de la demodulación (señales Q e I) hacia la PC para ser procesados y mostrados en un ambiente gráfico. El procesador MB ha sido programado convenientemente para controlar todo este proceso.

Al sintetizar el módulo IP del Lazo de Costas fue necesario disminuir el número de datos de la memoria ROM asociados a los osciladores locales NCO hasta 4096 datos, para así reducir el número de bloques de memoria BRAM consumidos por el módulo IP a 10 bloques. Teniendo en cuenta que la implementación del procesador MB y sus periféricos consumen otros 8 bloques adicionales, el diseño puede ser implementado en los 28 bloques disponibles para el procesador FPGA de la tarjeta Nexys2 empleada. Esta decisión hace que la resolución en frecuencia del oscilador local se empeora hasta 10.7 Hz, sin embargo teniendo en cuenta que los niveles de la frecuencia central del oscilador se encuentran en la banda de audio, alrededor de los miles de Hz, son suficientes para una correcta demodulación como se presenta en la simulación de figura, donde se exponen los resultados similares obtenidos en la demodulación con resoluciones de 16 y 12 bits en memoria ROM para una misma señal BPSK.

En la figura 11 se presentan los resultados finales obtenidos en la demodulación de una señal psk mediante una comparación de las señales I obtenidas mediante simulaciones con Simulink y XSG y las señales procesadas por el módulo IP.

La disminución de los niveles de voltaje de las señales obtenidas en XSG y el módulo IP respecto a la señal simulada se debe a la diferencia en la precisión de la aritmética usada de punto fijo sfix(16,15). Se aprecia también una disminución en el nivel de la señal obtenida por el IP, aunque es suficiente para ser detectada por la etapa de toma de decisión para la obtención de la secuencia de bits.

El uso de la herramienta XGS para la generación de módulo IP del Lazo de Costas ha sido muy efectiva, teniendo en cuenta las posibilidades que la misma brinda al estar integrada en el ambiente Simulink de Matlab, se han podido realizar simulaciones con modelos en aritmética flotante y exportarlos directamente con aritmética punto fijo a un sistema FPGA. Esto ha facilitado el diseño al reducir el tiempo de diseño de la aplicación total. La síntesis del módulo IP se realiza en unos pocos minutos, generando los ficheros de aplicaciones y de documentación que facilitan la integración del módulo en el procesador en cuestión.

Conclusiones

La implementación de un módulo IP del circuito Lazo de Costas para la demodulación de señales BPSK, diseñado con la herramienta XSG sobre Matlab, ha sido comprobada mediante simulación en el ambiente Simulink de Matlab y de manera práctica mediante una aplicación de un procesador MicroBlaze que emplea dicho módulo. Se ha logrado la demodulación de BPSK señales con altos niveles de ruido y características extremas de modulación con tiempos de símbolo del orden del período de la portadora, para frecuencias de muestreo en la banda de audio, no superiores a 44 kHz. El uso de la simulación del modelo de Costas es fundamental ya que no existen modelos analíticos suficientemente exactos del mismo. Mediante simulaciones previas se pueden determinar adecuadamente los parámetros del Lazo de Costas para el módulo IP, Para implementar el procesamiento señales M-PSK con módulos IP basados en el Lazo de Costas se necesita una familia FPGA de mayores recursos ó valorar el uso de otras arquitecturas de más eficiencia de recursos tales como módulos IP de síntesis directa DDS o un bloque CORDIC. Aunque la síntesis del módulo IP del Lazo de Costas con los parámetros necesarios para demodular una cierta señal BPSK consume poco tiempo, se recomienda trabajar en una estructura de módulo IP con parámetros genéricos que facilite su uso para cualquier señal.

1. Tuttlebee W. "Software Defined Radio. Origins" Wiley. 2002.ISBN 0470 84464 7. [ Links ]

2. Lay, E. "Practical Digital Signal Processing". Newnes. Elsevier, 2003. [ Links ]

3. "DigilentNexys 2. Reference Manual". January 21, 2008. [ Links ]

4. Haykin S. "Communication Systems". Fourth edition, Prentice Hall, 2000. [ Links ]

5. Feigin J. "Practical Costas loop design". www.rfdesign.com, January 2002. [ Links ]

6. Costas J.P. "Synchronous Communication". Proc. Of the IEEE, Vol. 90, Nº 8, August 2002. [ Links ]

7. Ginori Juan V. Lorenzo. "Equipos Electrónicos para la Transmisión de Datos", segunda edición. [ Links ]

8. F. M. Gardner. "Phase lock Technique", Wiley, New York, 1979. [ Links ]

9. Yuan, H.; Hu, X.; Huang, J. "Design and Implementation of Costas LoopBased on FPGA", Universidad de Valladolid, 2010. [ Links ]

10. M. Xiaoand, T. Cheng. "Improved implementation of Costas Loop for dqpskreceivers using fpga", Int. Conf . on Comm. Tech. (ICCT), 2006. [ Links ]

11. Bar-Giora Goldberg. "Digital Frequency Synthesis Demystified". LHH Technology Publishing, 1999. [ Links ]

12. Stewart B. et al. "DSP for FPGA Primer". University of Strathclyde. Glascow. 2011. [ Links ]

13. Mathworks. "Processor examples: Creating MicroBlaze Peripherals in System Generator".XGS. Additional examples. Matlab 2009b. [ Links ]

14. Torres Gomez, J. "Demodulación asincrónica de señales BFSK mediante el receptor de correlación con técnicas digitales". Departamento de Telecomunicaciones y Telemática, Facultad de Ingeniería Eléctrica, ISPJAE, 2012. [ Links ]

Recibido: 07/10/2013

Aprobado: 20/02/2014